学习笔记-2022.1.13

1. 半导体模拟集成电路-XJTU 张鸿教授 第一章 集成电路介绍

1.研究模拟电路重要性

- 自然界信号的处理

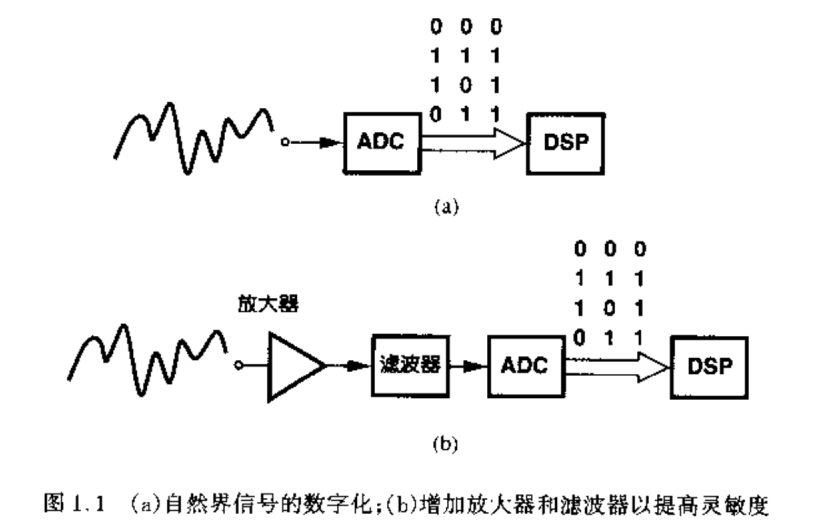

自然界产生的信号在宏观上是模拟量。如麦克风接受乐队声音、照相机中光电池的电流等。所有这些信号都需要在数字领域进行多方面处理,这样的系统需要一个模数转换器(ADC)和数字信号处理器(DSP)组成。高速、高精度 、低功耗ADC设计是模拟电路设计中的众多难题之一。

- 数字通信

不同系统产生的二进制数据往往需要传输很长的距离,但若是使用电缆会出现衰减和失真,此时需要采用类似图1.1(b)的接收器。

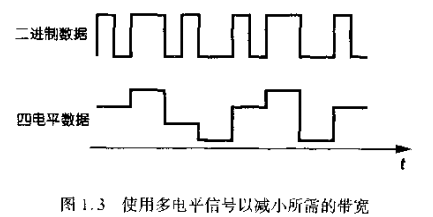

现代通信系统广泛采用多电平信号,在发射中需要数模转换器把组合的二进制数据转换为多电平信号,而在接受器中使用模数转换器确定所传输的电平。

- 磁盘驱动电子学

计算机硬盘中的数据采用此行原理以二进制形式存储,然鹅在数据被磁头读取并转换为电信号时,复读只有几毫伏且噪声含量搞,信号需要被放大、滤波以及数字化,此时模拟滤波器可以依靠系统整体结构消除信号中的主要噪声和失真。

- 无线接收器

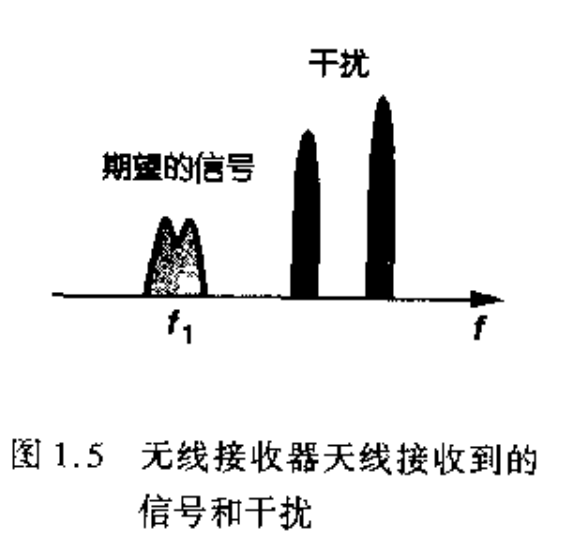

射频接收器(RF)的天线接收到的信号幅度只有几毫伏,而中心频率达到1GHz甚至更高,且信号伴有很强的干扰。此时接收器在放大低电平信号时必须具有极小噪声、工作在高频并能抑制大的有害分量。

- 光接收器

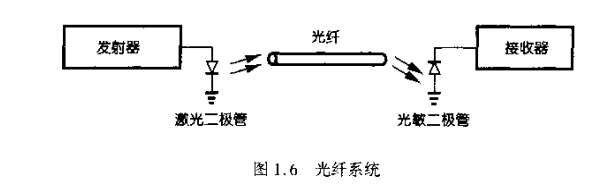

高速数据远距离传输时,数据在由激光二极管转换为光后通过光纤传输,接收端通过光敏二极管转换为小电流。

- 传感器

- 微处理器和存储器

许多涉及到大规模芯片内部或不同芯片之间的数据时钟的分布和时序问题要求将高速信号座位模拟波形处理,而且芯片上信号间和电源间互联中的非理想性以及封装寄生参数要求对模拟电路设计有完整的理解。半导体存储器广泛使用的“读出放大器”也不可避免的设计许多模拟技术。

2. 模拟技术的难点

- 模拟设计涉及速度、功耗、增益、精度、电源电压等多种因素折衷,数字电路基本上只需在速度和功耗之间折衷。

- 模拟信号处理过程中要求速度和精度的同时,模拟电路对噪声、串扰和其他干扰比数字电路敏感的多

- 器件的二级效应对模拟电路影响比数字电路性能影响严重的多

- 高性能模拟电路很少能够自动完成,数字电路多可以自动综合布线

- 模拟电路许多效应的建模和仿真仍存在难题

- 现代半导体工业的一个重要目标是用制造数字产品的主流集成电路技术来设计模拟电路,它们不容易被模拟电路设计所利用

3. 电路设计的一般概念

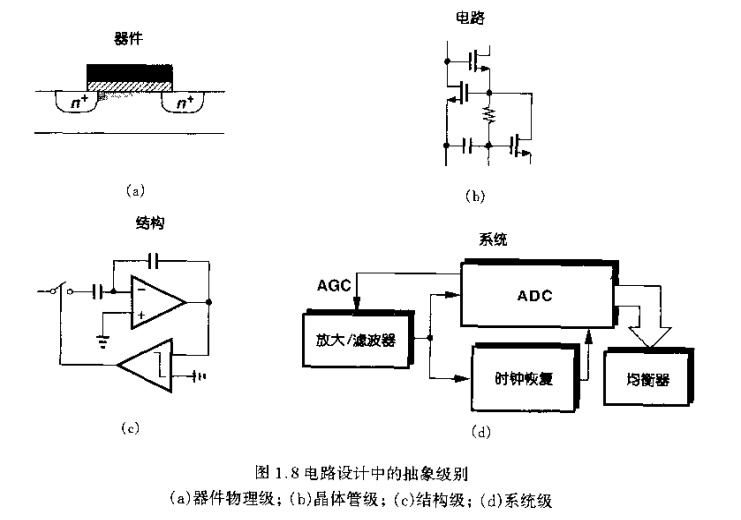

- 抽象级别

- 符号

1. 半导体模拟集成电路-XJTU 张鸿教授 第二章-1 MOS器件物理

1. MOSFET的结构

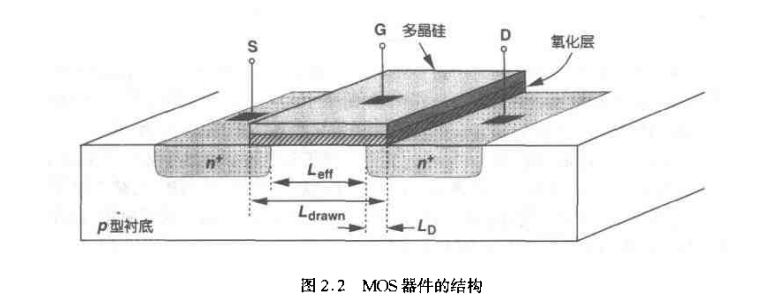

NMOS器件的简化结构如图2.2。器件制作在p型沉底(称作bulk或者body),两个重参杂n区形成源端和漏端,一层薄SiO2使栅和衬底分离。这种结构中源和漏对称。

源漏方向的栅的尺寸叫栅长L。与之垂直方向的栅的尺寸叫做栅宽W,由于制造过程中源漏结横向扩散,源漏之间实际长度略小于L,我们定义Leff=Ldrawn-2LD,工艺中的.18μm中的0.18主要是指Ldrawn,通常工艺中W=L。

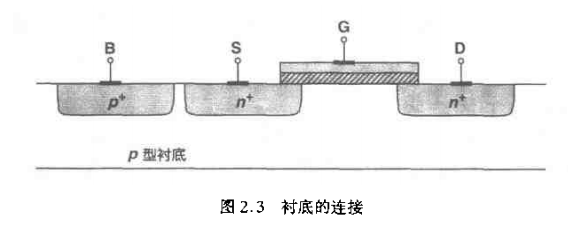

器件衬底电位对器件特性有很大影响,也就是说MOSFET是一个四端器件,典型MOS工作中,源/漏接二极管都必须反偏,所以NMOS晶体管衬底被连接到系统最低电压上,通常为0。

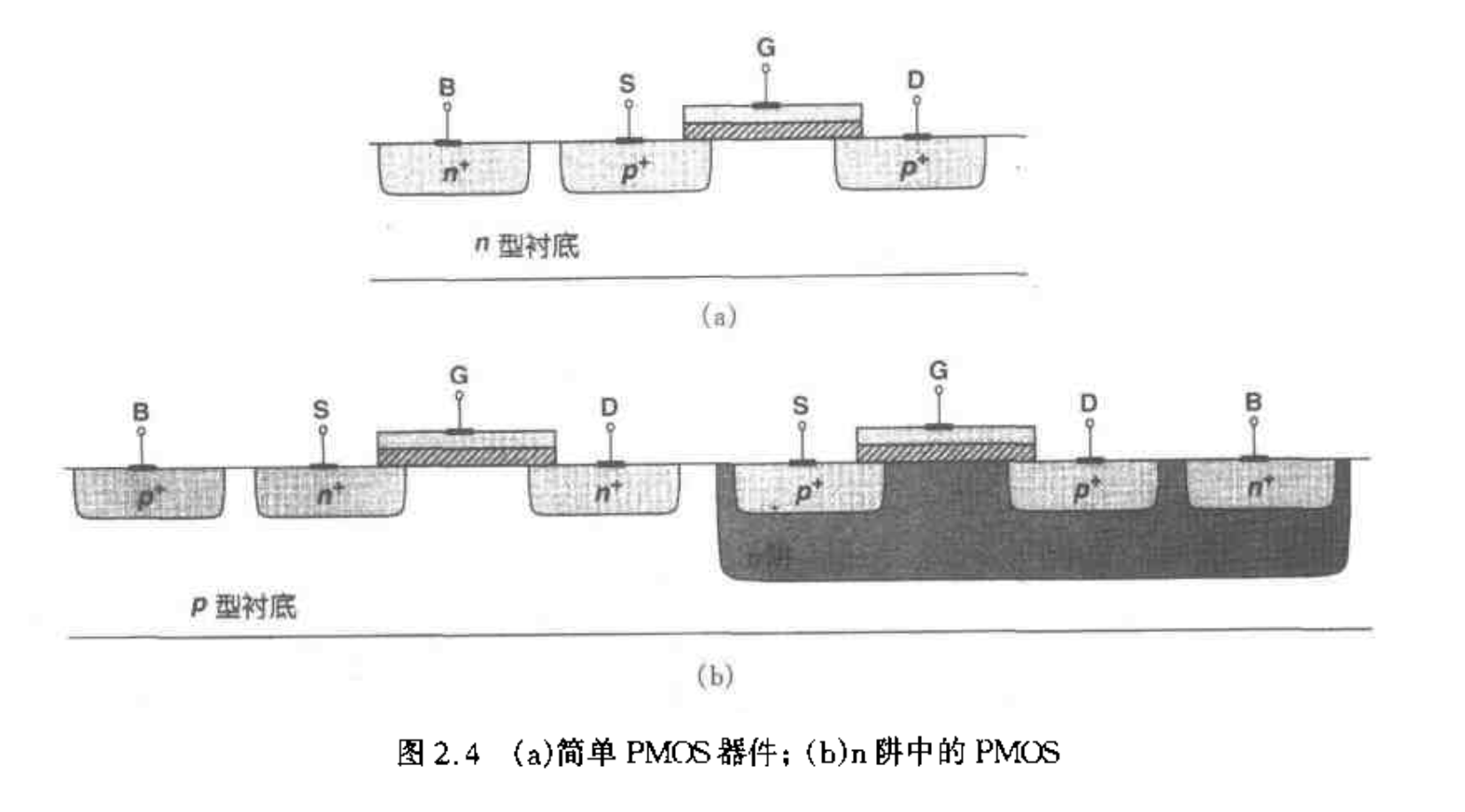

在CMOS技术中需要同时用到NMOS和PMOS。从简单的角度来看,PMOS器件可通过将所有掺杂类型取反(包括衬底)来实现。但实际生产时NMOS和PMOS必须做在同一晶片上,故某一种类型的器件要做在一个局部衬底上,通常称为“阱”。现在大多数CMOS工艺中,PMOS管坐在n阱中(图2.4b)大多数电路中n阱与最正的电源相连接。简化有时分别称NMOS和PMOS器件为“NFETS”和“PFETs”。

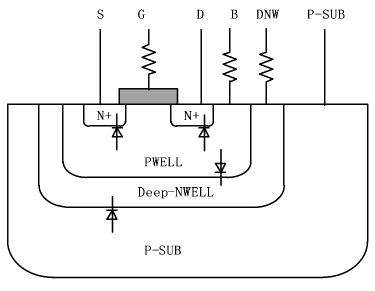

这种情况下,所有NMOS的衬底都接在一起,通常接地,而统一n阱内的PMOS必须接同一电位,不同n阱中的PMOS可以接在不同电位。而由于所有NMOS衬底接在一起,会有crosstalk效应,即一只晶体管的扰动回影响其他晶体管,现在通常使用deep n-well来解决这一问题。

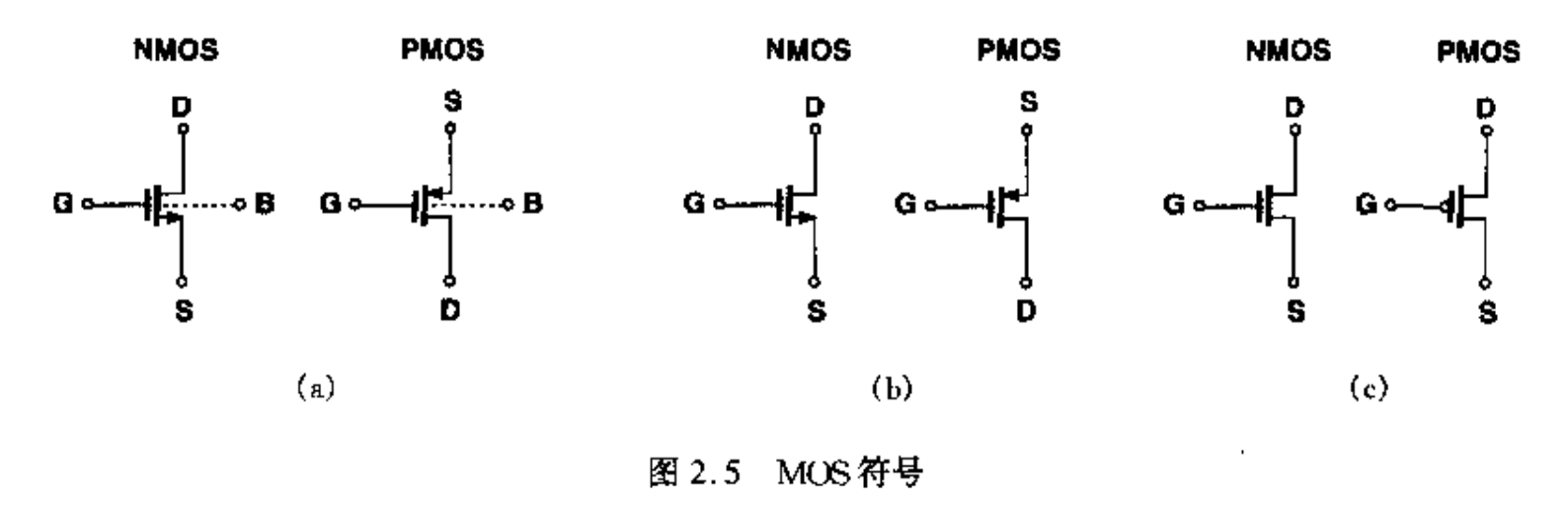

2. MOS符号

在数字电路中习惯用图2.5c所示的开关符号来表示两种MOS管,但模拟电路设计时更喜欢用2.5b表示,因为明确区分源漏对于理解电路的工作很有帮助。

3. MOS的I/V特性

- 阈值电压

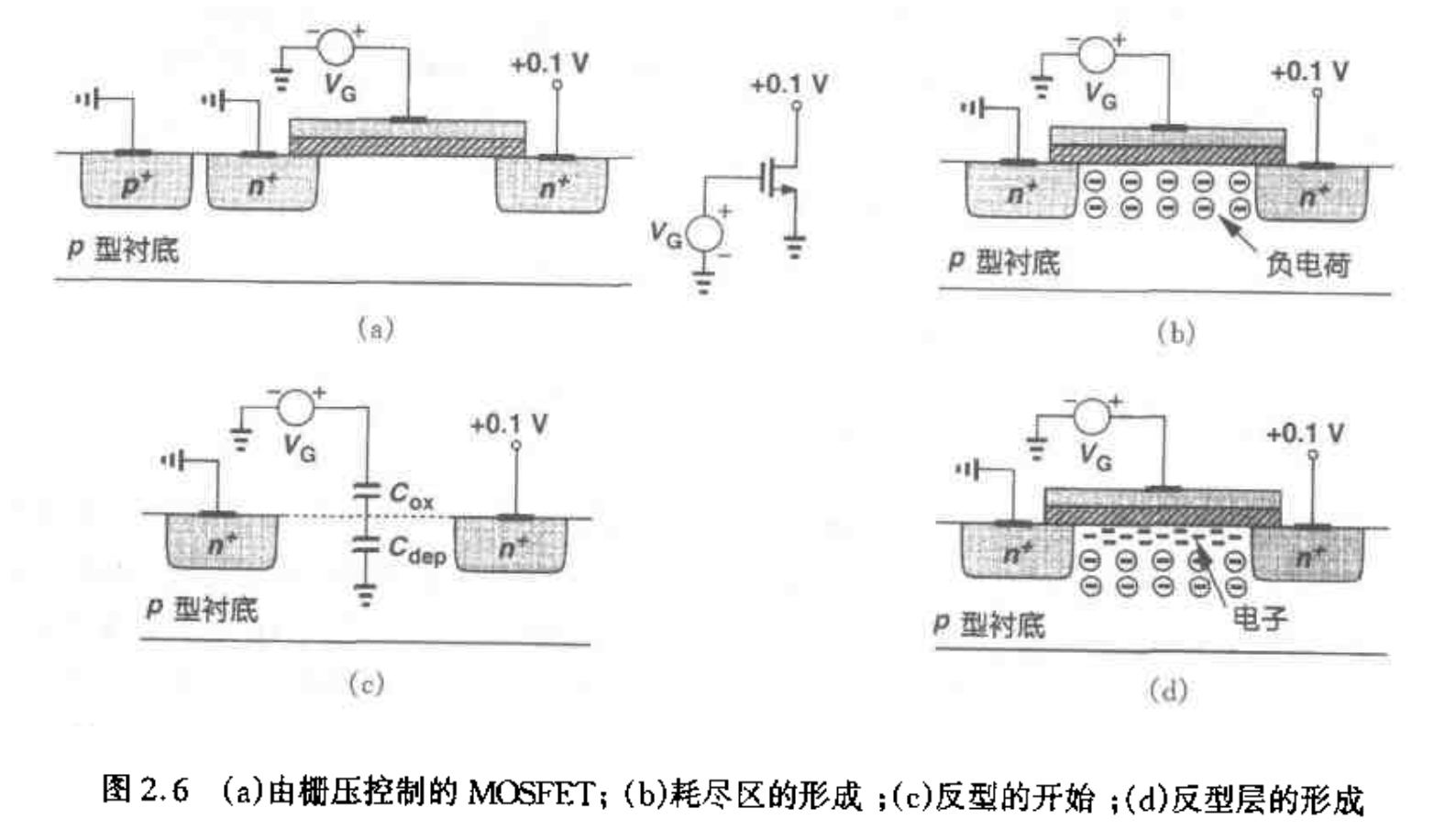

当栅压VG 逐渐升高时,p衬底的空穴被赶离栅区而留下负离子以镜像栅上的电荷,相当于形成了耗尽层(图2.6b)但此时由于没有载流子而无电流流动。随着VG继续升高,耗尽层宽度和氧化为与硅界面处电视也增加,这相当于连个电容的串联(图2.6c),其中Cox为固定点人。Cdep为可变电容。当界面电势足够高时,电子便从源流向界并最终流入漏端,源漏之间形成载流子沟道,晶体管导通,我们称之为“反型”,形成沟道对应的VG成为“阈值电压”或VTH,如果VG进一步升高,则耗尽区电荷保持相对恒定,沟道电荷密度继续增加,导致源漏电流增加。

在报道题为力学中,NFET的VTH通常定义为界面的电子浓度等于p型衬底的多子浓度时候的栅压。

其中$\varPhi {MS}$是多晶硅栅和硅称帝功函数之差,$\varPhi {F}=(kT/q)ln(N{sub}/n{i})$,$q$是电子电荷,$N_{sub}$是衬底掺杂浓度,$Q_{dep}$是耗尽区电荷,$C_{ox}$是单位面积的栅氧化层电容,$Q_{dep}=\sqrt{4q\varepsilon {si}|\varPhi F|N{sub}}$,其中$\varepsilon{si}$为硅的介电常数,$C_{ox}=(\varepsilon_{si}\varepsilon_{0})/t_{ox}$。

由公式可得到规律:$t_{ox}\downarrow \rightarrow V_{TH} \downarrow$ ,$N_{sub}\downarrow \rightarrow V_{TH} \downarrow$ ,温度也会影响$V_{TH}$,通常$T\downarrow \rightarrow V_{TH} \downarrow$ 。

- I/V公式推导

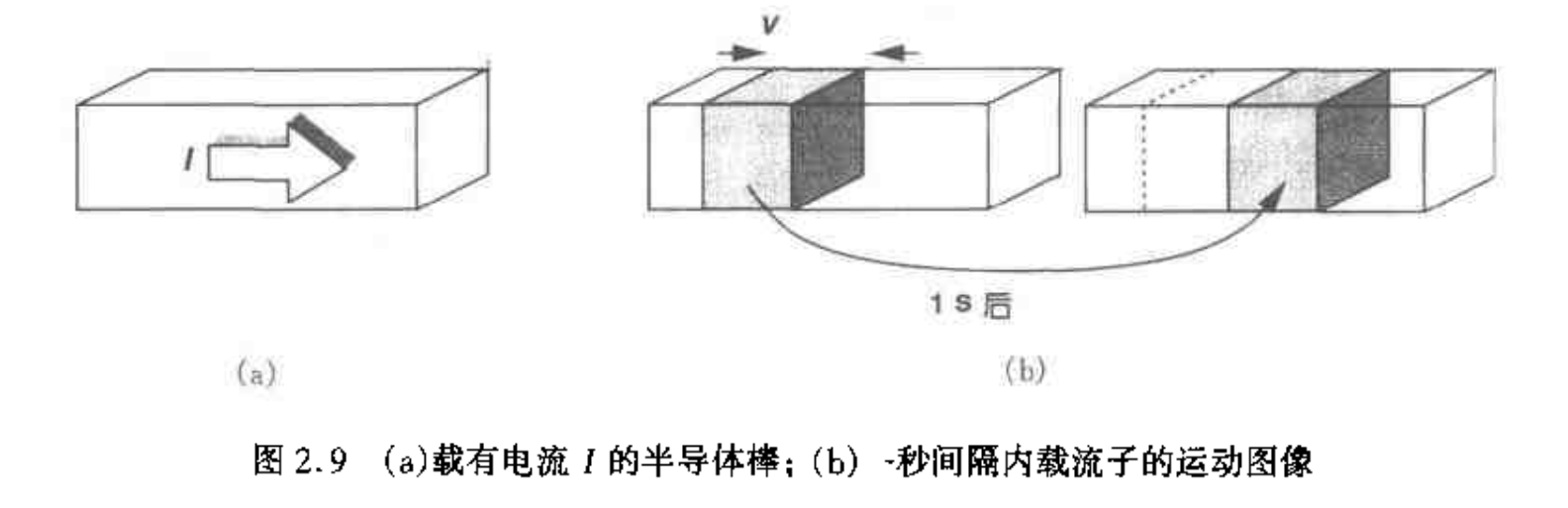

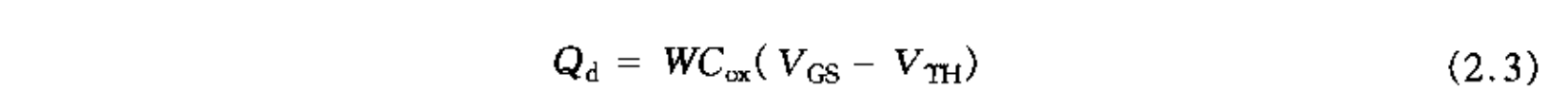

首先有个先导公式:

其中电流方向的电荷密度为$Q_{d}$,电荷移动速度为$v$。

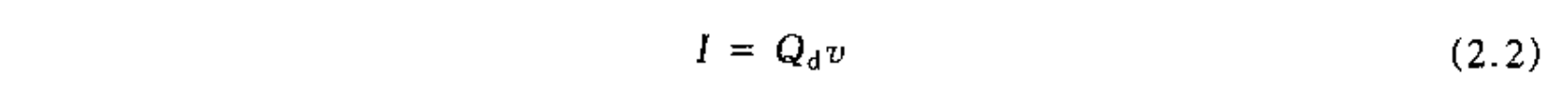

当$V_{GS}=V_{TH}$时开始反型,由栅氧化层电容引起的反型电荷密度正比于$V_{GS}=V_{TH}$,当$V_{GS}>V_{TH}$时,栅电荷被沟道电荷镜像,从而产生均匀的沟道电荷密度(单位长度电荷),其值等于

式中,$C_{ox}$与$W$相乘表示单位长度的总电容。

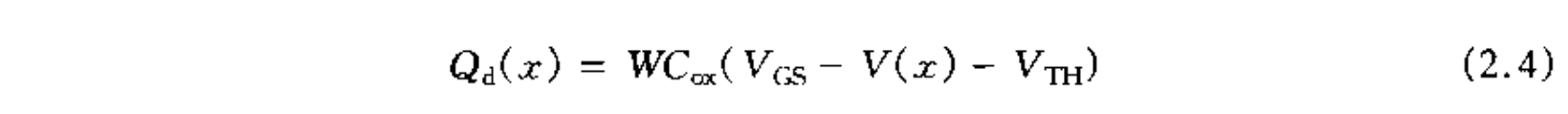

如图2.10b,假设漏极电压大于0,沟道电势从源的0V到漏极Vd,栅与沟道局部电压差从VG变化为VG-VD,沟道x处电荷密度为:

V(x)为x点沟道电势。

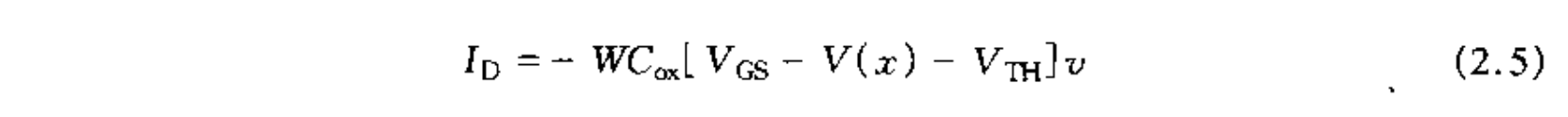

电流为:

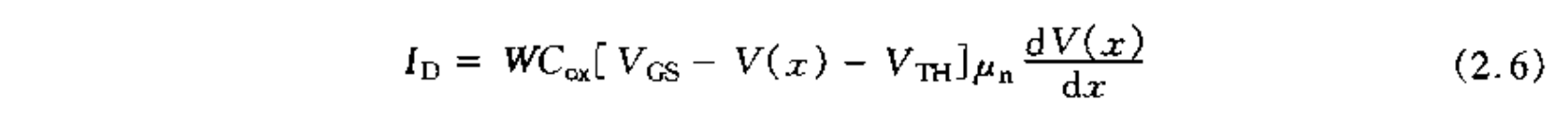

对于半导体。$v=μE$,$E(X)=-dV/dX$,故:

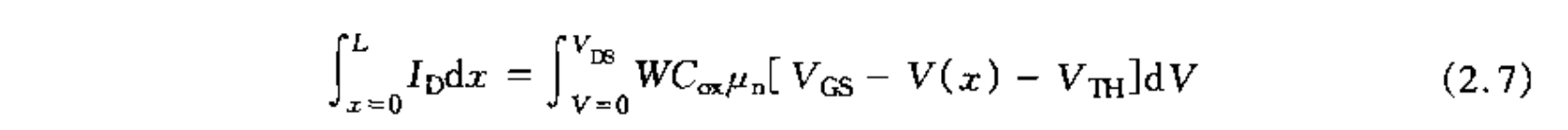

对V(0)=0到V(L)=VDS积分可得:

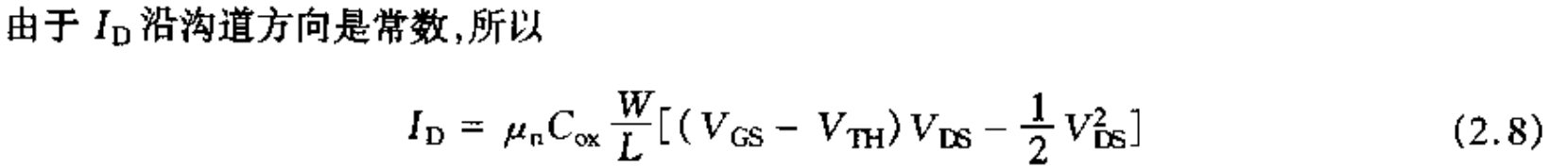

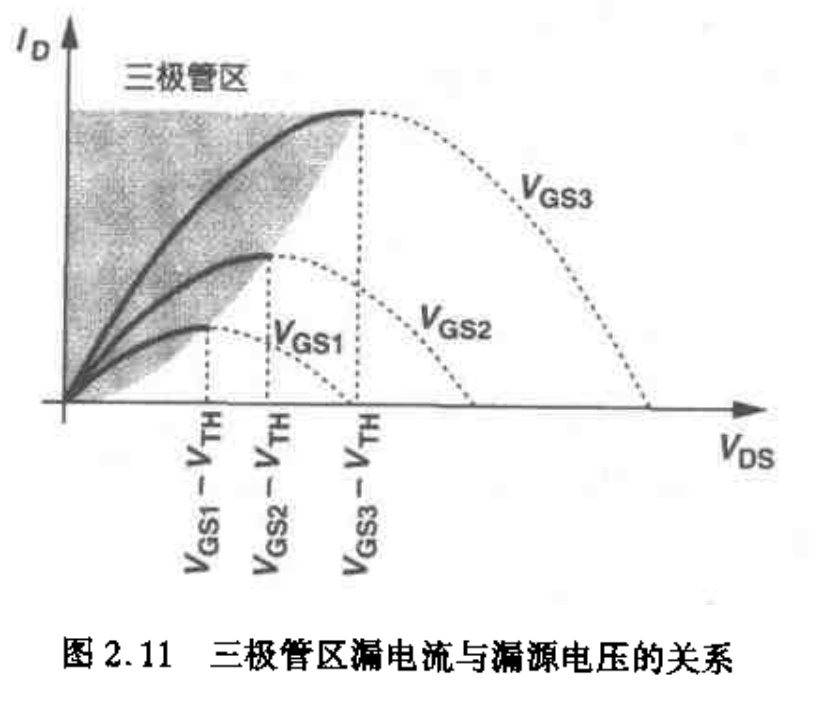

$V_{GS}-V_{TH}$为“过驱动电压”,$W/L$为宽长比。若$V_{DS}<V_{GS}-V_{TH}$,则器件工作在“三极管区”

式中设计者可以调整的参数为$W/L$以及$V_{DS}$式中其他变量均为器件定值或者工艺定值,设计者无法调整。

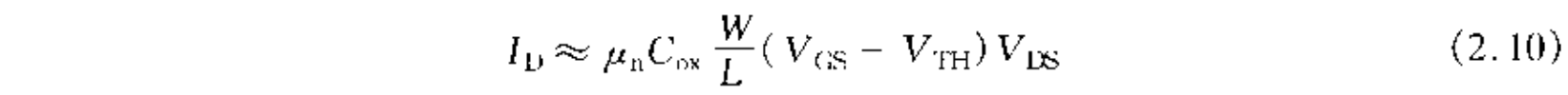

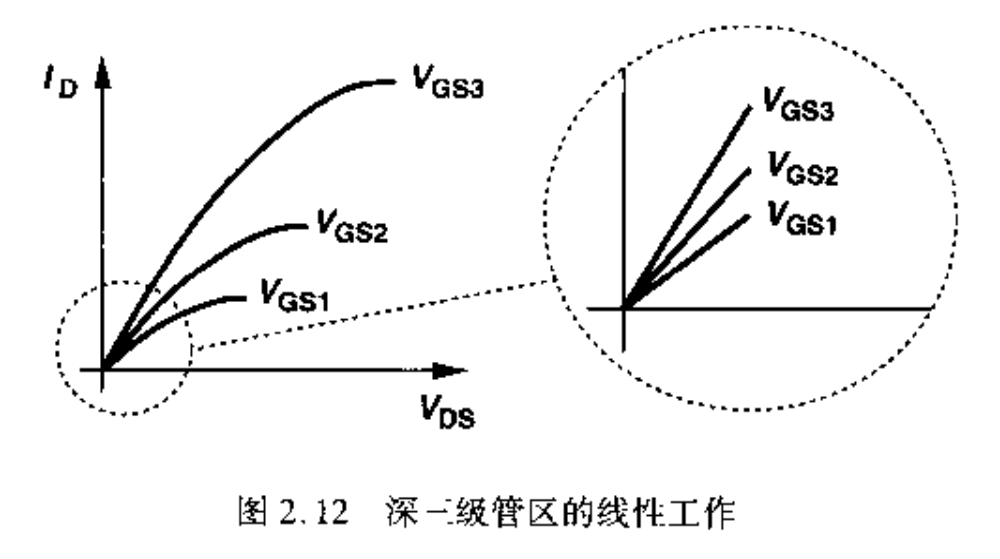

当$V_{DS}<<2V_{GS}-V_{TH}$时有

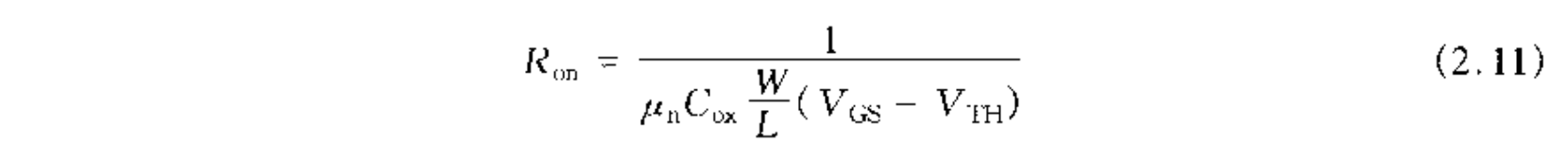

此时可用线性函数近似代替,源漏通道表现为一个线性电阻,此时MOSFET就可以作为一个阻值由过驱动电压控制的电阻,阻值为:

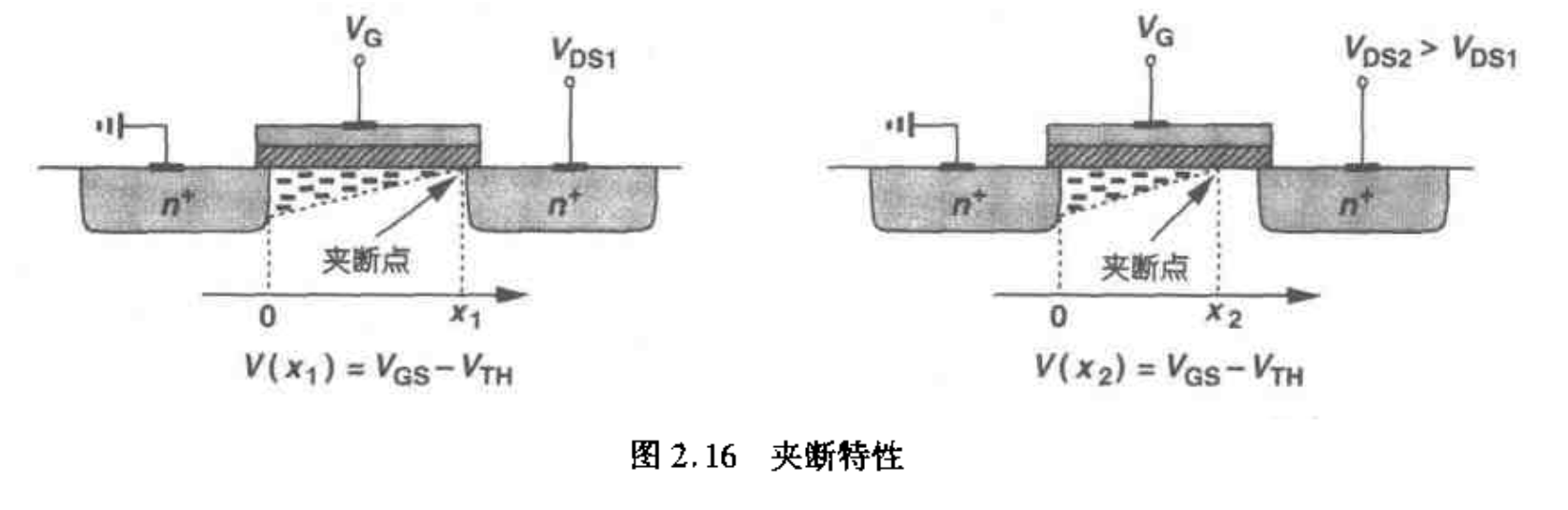

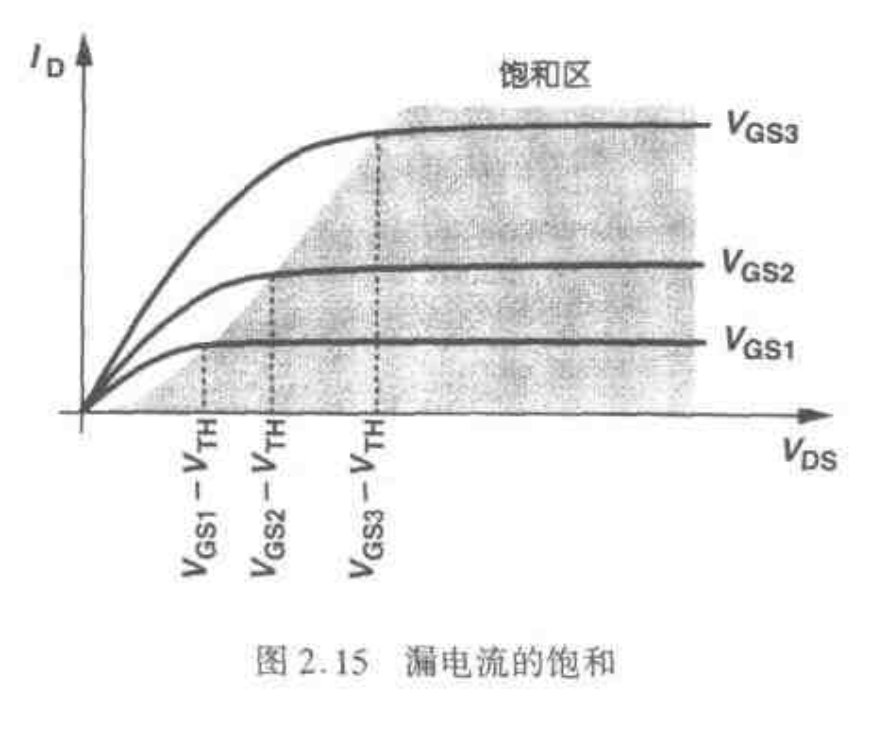

继续增大$V_{DS}$当$V_{DS}>2V_{GS}-V_{TH}$s时,此时$I_{d}$相对恒定,器件工作在饱和区,反型层将在$x<=x$处终止,我们认为沟道为夹断。

此时看式2.7可得:

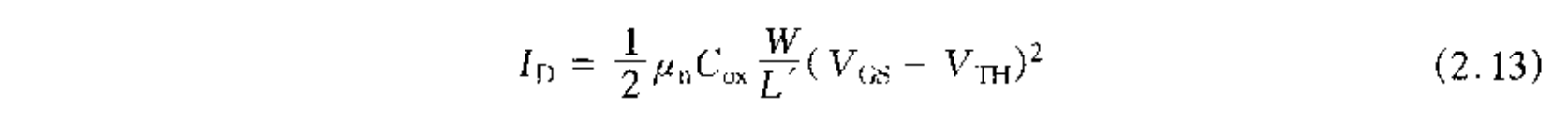

对于PMOS:

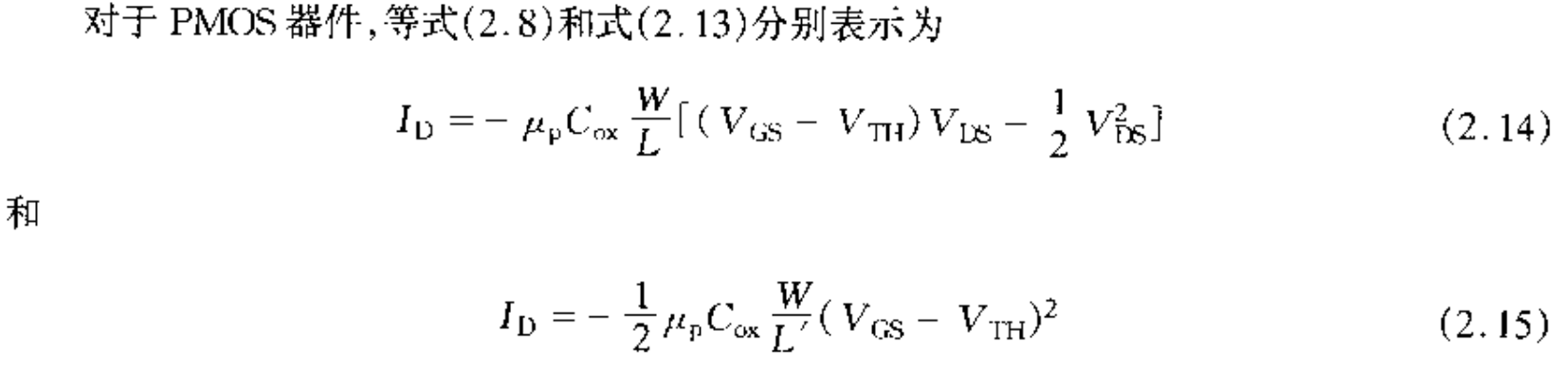

此时可认为工作在包河区的MOSFET构成一个连接源和漏的电流源,电流源的特点为电流与两端电压无关。此电流源仅与过驱动电压有关,可以说受过驱动电压控制